## The CASE of FEMU: Cheap, Accurate, Scalable and **Extensible Flash Emulator**

Huaicheng Li, Mingzhe Hao, Michael Hao Tong, Swaminatahan Sundararaman\*, Matias Bjørling<sup>+</sup>, Haryadi S. Gunawi

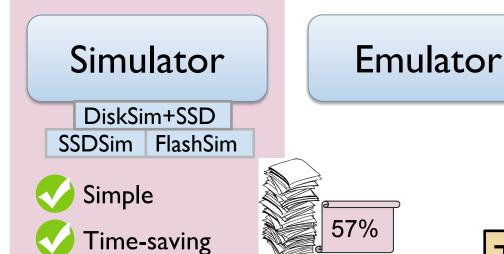

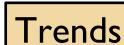

## What SSD platforms are used?

Trace driven

only

Internal-research

Hardware Platform

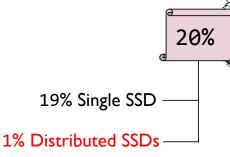

- Software-Defined Flash

- Split-Level Architecture

#### Simulator

DiskSim+SSD SSDSim FlashSim

Simple

Time-saving

Trace driven

Internal-research only

#### **Emulator**

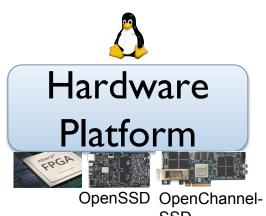

## Hardware Platform

Complex to use

#### Simulator

DiskSim+SSD

SSDSim FlashSim

Time-saving

Trace driven

Internal-research only

#### **Emulator**

LightNVM's QEMU VSSIM FlashEm

**Cheap**

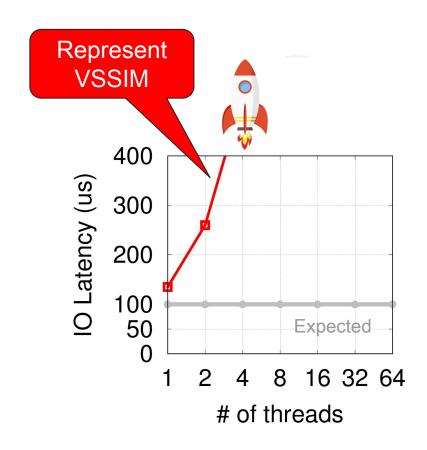

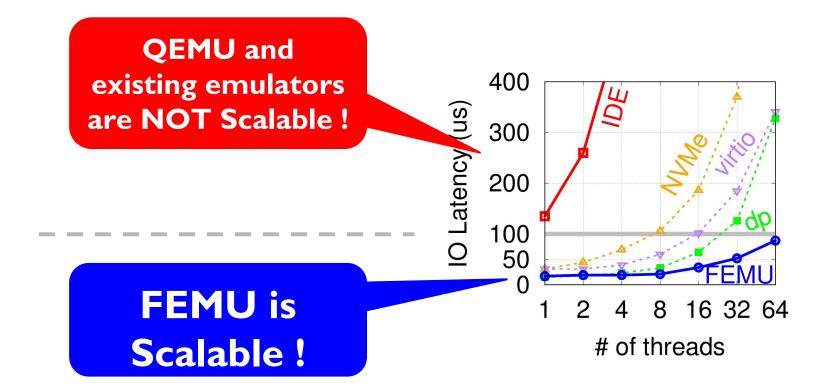

Poor Scalability

Poor Accuracy

Full-stack Research

Accurate

Expensive

Complex to use

🔃 Wear-out

#### The "CASE" of FEMU

FEMU: QEMU/Software based Flash Emulator

- ☐ Cheap: \$0, https://github.com/ucare-uchicago/femu

- ☐ Accurate: 0.5-38% error rate in latency

- ☐ II% average at microsecond level

- ☐ Scalable: support 32 channels/chips

- Extensible

- modifiable interface

- modifiable FTL

## What is FEMU?

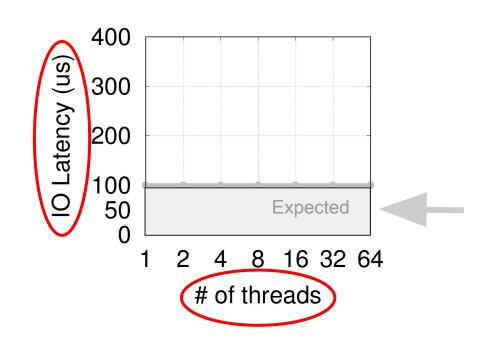

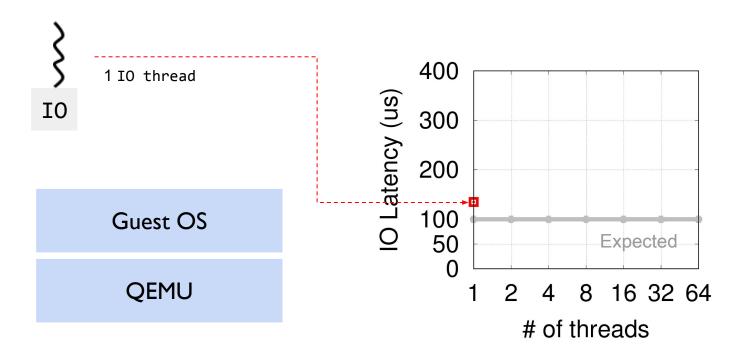

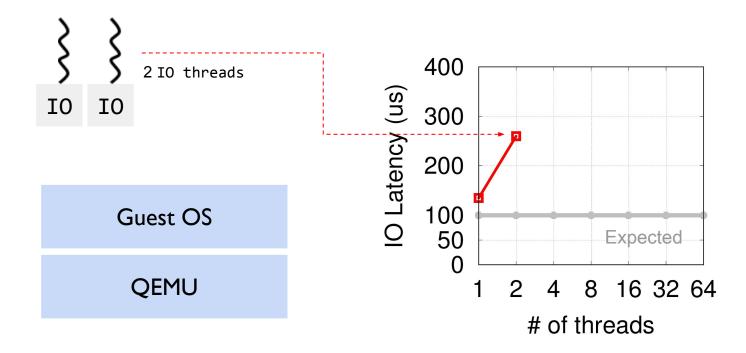

#### **QEMU Scalability**

**Guest OS**

**QEMU**

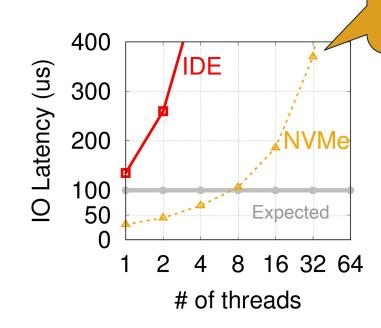

## **QEMU IDE Scalability**

**Guest OS**

**QEMU**

## **QEMU NVMe Scalability**

**Guest OS**

**QEMU**

Represent LightNVM's QEMU

## **QEMU Scalability**

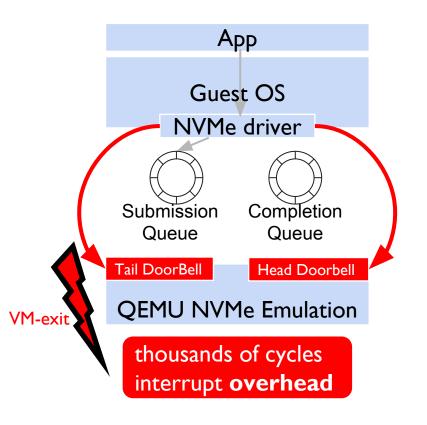

## Scalability Root Causes & Solutions (1)

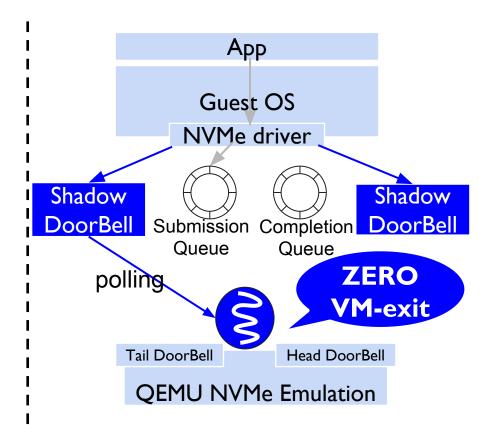

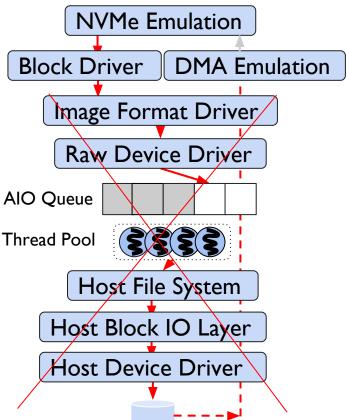

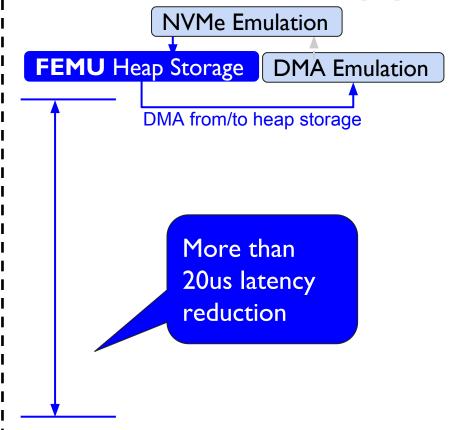

Scalability Root Causes & Solutions (2)

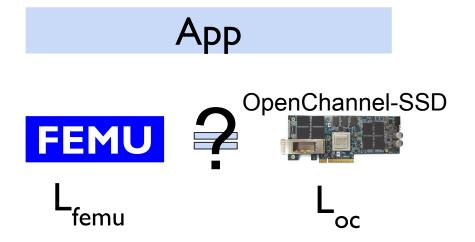

## **FEMU Accuracy**

Error =

$$|L_{femu} - L_{oc}| / L_{oc}$$

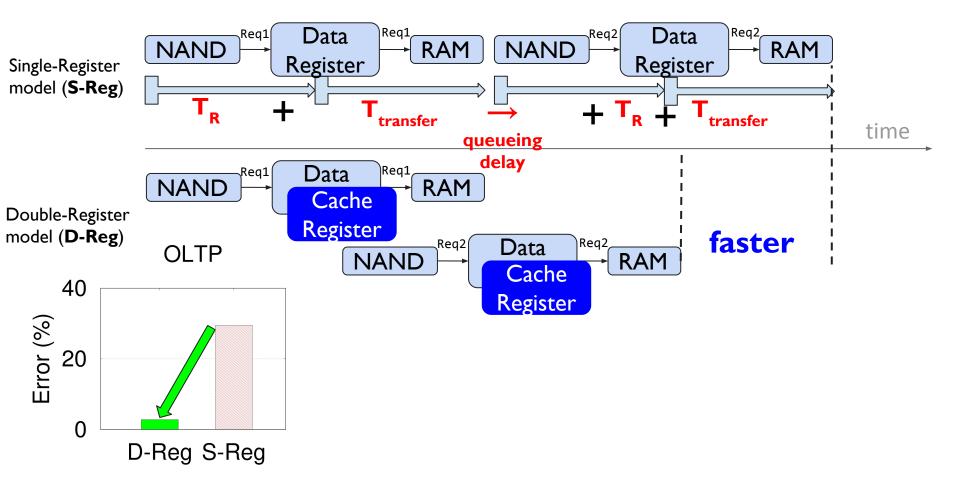

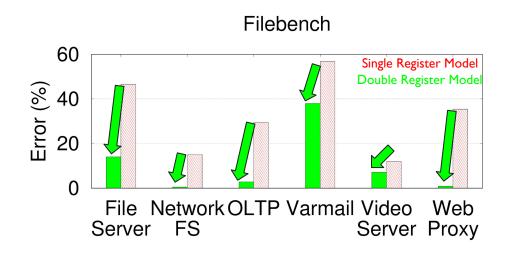

#### **FEMU Accuracy**

Latency Error: 11-57%  $\Rightarrow 0.5-38\%$

Single Register

Model (S-Reg)

Double Register

Model (D-Reg)

X: # of channels Y: # of planes per channel

#### **FEMU Limitations**

- Further optimizations to support higher parallelism (more scalable)

- Accuracy can be improved

- Not able to emulate large-capacity SSD

- No persistence

# Thank you! Questions?

FEMU: https://github.com/ucare-uchicago/femu